高通分享為何掌握越多自研架構對高通發展裝置智慧更為重要,以及實體AI對於多SoC或SoC搭配加速器的抉擇

在高通2026年的媒體春酒,筆者與同桌的台灣高通人員聊到高通目前的策略布局,由於並非正式的訪談,也是與不僅一位交流的內容,所以就不列出受訪者,提到包括高通在邁入自主CPU架構後於SoC設計自主權的重要,高速通道技術的影響,以及於實體AI架構設計的多SoC或SoC搭配加速器的抉擇。

自主CPU微架構突破授權微架構設計限制提升擴展性

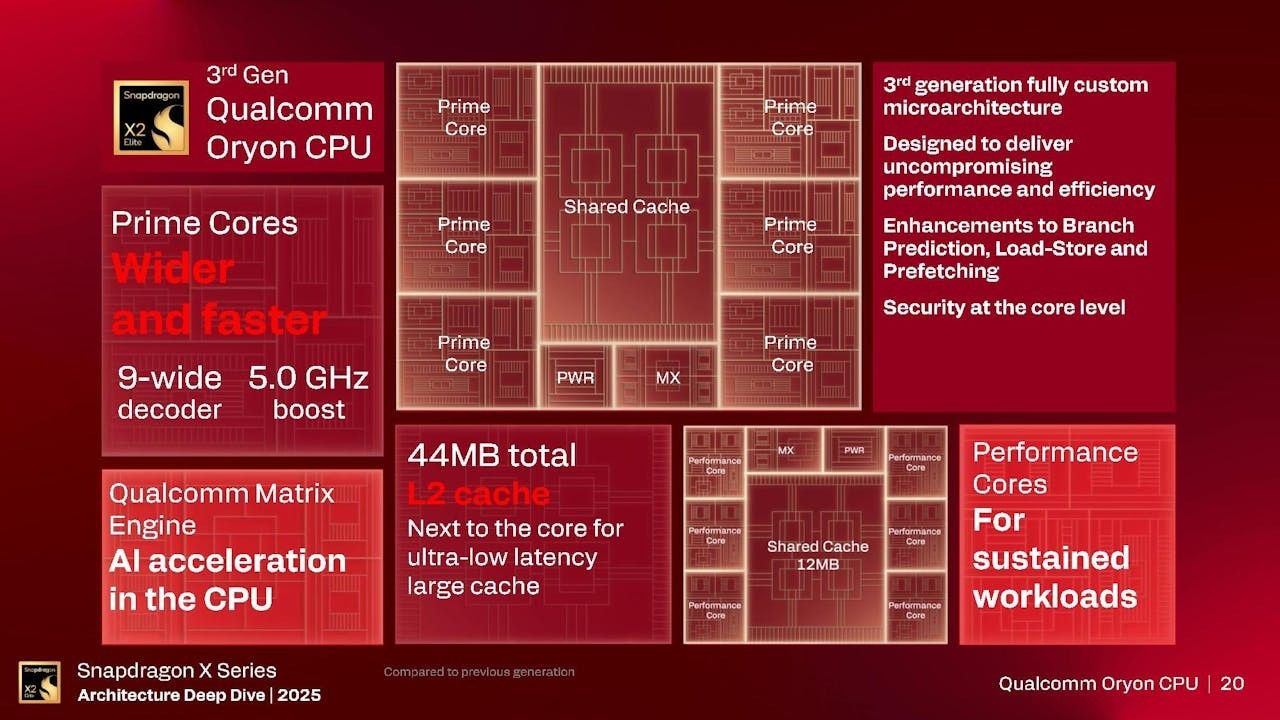

高通人員提到,高通原本就掌握網通、GPU與NPU架構自主設計能力,然而自與Arm合作採用Cortex微架構轉向自研的Oryon CPU架構,對於高通在產品與技術的擴展相當重要,透過掌握自主的微架構設計,高通得以結合長年在行動運算的經驗與對不同領域運算需求的洞察,不僅可量身設計能源效益及效能更佳的微架構。

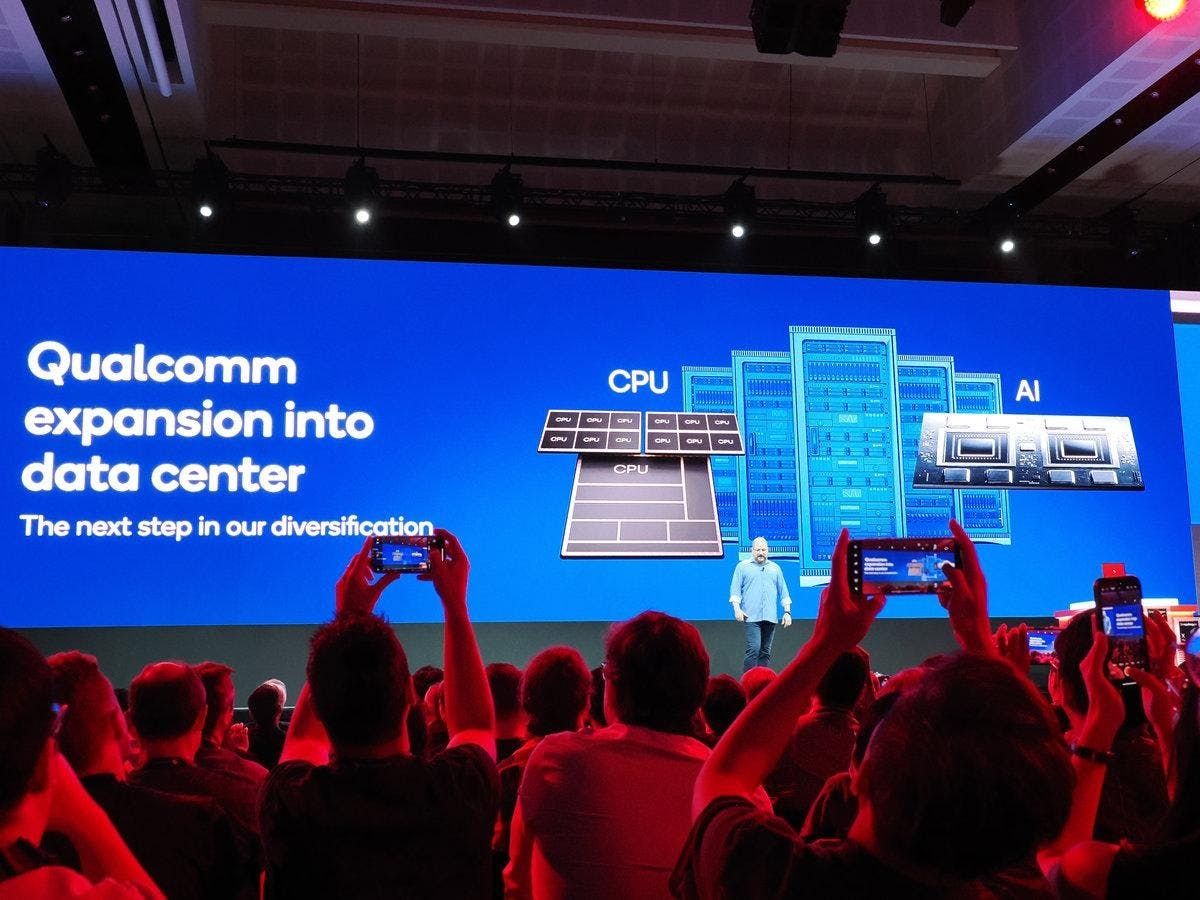

同時高通在SoC內也導入模組化的設計,即便並非小晶片,透過將架構設計模組化,高通能夠因應不同的算力、運算需求進行擴展,在目前Snapdragon手機平台、Snapdragon X PC平台甚至Dragonwing平台,高通正活用這項優勢規劃產品,預期後期的新一代資料中心產品也會延續這項策略。

裝置端結合高速通道的進行擴展的理由

因為筆者留意到高通先前公布Dragonwing IQ10平台時,描述中提到Dragonwing IQ10可透過擴充加速器提升AI TOPS,也向高通問及相關技術;高通人員表示這是受惠於Dragonwing IQ10搭載高速的PCIe通道,故可搭配高通的AI加速器產品進一步擴充性能。

在工業物聯網、自主AI等裝置端AI的需求與資料中心、伺服器仍有所不同,符合經濟效益、通用的PCIe通道技術仍扮演重要的角色,透過高通SoC與加速器的組合,能夠進一步針對需要更複雜AI推論的應用情境獲得合宜的效能,且相對直接SoC化則提供對於不同算力的彈性,畢竟不是所有的工業應用都需要700 AI TOPS的NPU算力。

另一方面,高通在雲端高效能運算則宣布加入NVIDIA的NVLink Fusion陣容,在大規模高效能運算領域,高頻寬、低延遲的高速通道技術仍有其重要性,加上NVIDIA NVLink不僅具備超越PCIe規範的性能,同時也有經市場驗證的可靠性,此舉是作為高通因應目前高效能運算趨勢的彈性布局。

一個大腦搭配外掛或是多個大腦的不同情境需求

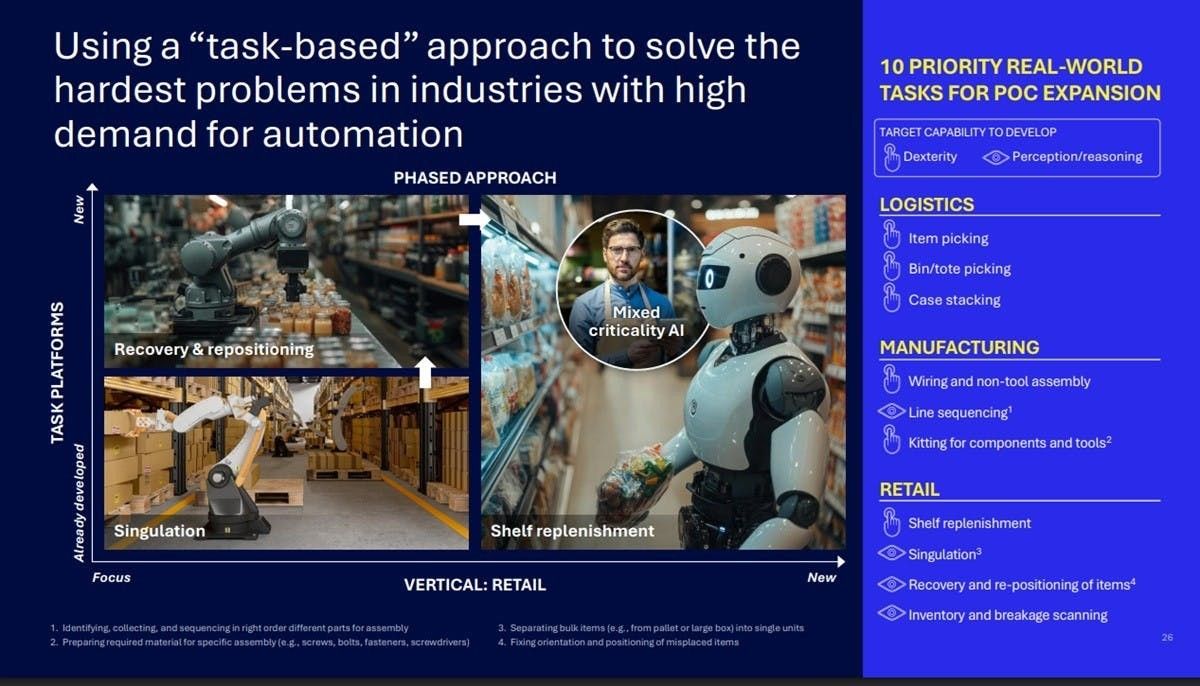

另外也提到在工業嵌入式、實體AI等,目前產業對於該使用多個大腦(SoC)或是由一個SoC搭配加速器的應用場景不盡相同,雖然透過單一個SoC搭配針對推論最佳化的加速器理論上有助發揮最大的能源效益,不過並不一定適用所有的應用情境,像這樣的組合也許適用機構較單純的實體AI設備或自主機器人。

不過如大規模影像處理應用、複雜結構自主機器人等應用,以多個SoC串接則有其意義;如大量、多路影像處理,由於每個SoC可以提供獨立的訊號輸入、編解碼,透過大量的SoC連接有助於迅速處理大量的影像內容,相對單一SoC搭配加速器或GPU更具優勢。

另一類多SoC組合的需求則是應用於具有複雜機構的自主機器人,這一類的應用可能會是由一顆頂級SoC負責主要運算與決策AI,搭配另一顆主要用於結合AI進行動作控制的高階處理器或即時處理器,利用兩個處理器相互協助取代單一處理器進行複雜混合任務的風險。